# L7585F Full-Feature, Low-Power SLIC and Switch

## Features

- Low active power

- Quiet tip/ring polarity reversal

- Distortion-free on-hook transmission

- 35 V to 60 V power supply operation

- 14 operating states:

- Forward battery active

- Reverse battery active

- Ground start (3)

- Forward battery ring open

- Reverse battery ring open

- Reverse battery tip open

- High impedance

- Ringing (2)

- Low current (2)

- Disconnect

- Self-test in all operating states

- Independent, adjustable ac and dc parameters:

Switchhook detector threshold

- Loop current limit

- dc feed resistance

- Termination impedance

- Integrated ringing access relay

- Integrated test-in relay

- Integrated relay driver

- Integrated ring trip detector

- Thermal protection

- 44-pin, surface-mount, plastic package (PLCC)

## Description

The L7585F Full-Feature, Low-Power Subscriber Loop Interface Circuit (SLIC) and Switch integrates the battery feed, test access relay, and ringing relay that are necessary to interface a codec to the tip and ring of a subscriber loop into one low-power, low-cost package. It is built using a 90 V complementary bipolar (CBIC) process and a 320 V Bipolar-CMOS-DMOS (BCDMOS) process. The device is available in a 44-pin PLCC package.

The device can be connected directly to the Agere Systems Inc. T8531/T8532 16-Channel Programmable Codec Chip Set without the need for any ac interface components.

# **Table of Contents**

## Contents

## Page Figures

## Page

| Features1                                          |

|----------------------------------------------------|

| Description1                                       |

| Architectural Diagram                              |

| Pin Information                                    |

| Operating States7                                  |

| Forward Battery Active State7                      |

| Ground Start/Tip Open State7                       |

| Ground Start/Tip Ground State8                     |

| Forward Battery Ring Open State8                   |

| Ringing States (2)                                 |

| Disconnect State                                   |

| Forward Battery Low-Current Active State8          |

| High-Impedance States (2)                          |

| Reverse Battery Active State                       |

| Reverse Battery Tip Open State8                    |

| Ground Start/Tip Amplifier State9                  |

| Reverse Battery Ring Open State9                   |

| Reverse Battery Low-Current Active State9          |

| Absolute Maximum Ratings ( $T_A = 25 \ ^\circ C$ ) |

| Electrical Characteristics                         |

| On-State Switch V-I Characteristics                |

| Applications                                       |

| Tip/Ring Protection                                |

| NDET Under Fault Conditions                        |

| Power, Clocking, and Layout18                      |

| Ring Trip19                                        |

| False On-Hook Transients                           |

| Application Diagram                                |

| Outline Diagram                                    |

| 44-Pin PLCC                                        |

| Ordering Information                               |

|                                                    |

| Figure 1. Architectural Diagram               |  |

|-----------------------------------------------|--|

| Figure 2. 44-Pin Diagram (PLCC)               |  |

| Figure 3. On-State Switch V-I Characteristics |  |

| Figure 4. 16-Channel Line Card Solution       |  |

| •                                             |  |

## Tables

## Page

| Table 1. Pin Descriptions                                      | 5  |

|----------------------------------------------------------------|----|

| Table 2. B0—B3 Input State Coding                              |    |

| Table 3. B4—B5 Input State Coding                              |    |

| Table 4. Operating Conditions and Powering                     |    |

| Table 5. Ring Trip Detector                                    |    |

| Table 6. Battery Feed Characteristics                          |    |

| Table 7. Analog Signal Pins                                    |    |

| Table 8. Transmission Characteristics                          |    |

| Table 9. Data Interface and Logic (Logic Inputs                |    |

| [CLK, NCS, and B0–B5] and                                      |    |

| Outputs [NDET])                                                | 14 |

| Table 10. Timing Requirements (CLK, B0-B5,                     |    |

| and NCS)                                                       | 14 |

| Table 11. Relay Driver (RDO)                                   | 14 |

| Table 12. Ringing Return Access Switch (SW1)                   | 15 |

| Table 13. Test-In Access Switches                              |    |

| (SW3 and SW6)                                                  | 15 |

| Table 14. Tip and Ring Break Switches                          |    |

| (SW2 and SW4)                                                  | 16 |

| Table 15. Tip and Ring Feedback Switches                       |    |

| (SW2a and SW4a)                                                | 16 |

| Table 16. Ringing Access Switch (SW5)                          | 17 |

| Table 15. Tip and Ring Feedback Switches       (SW2a and SW4a) | 1  |

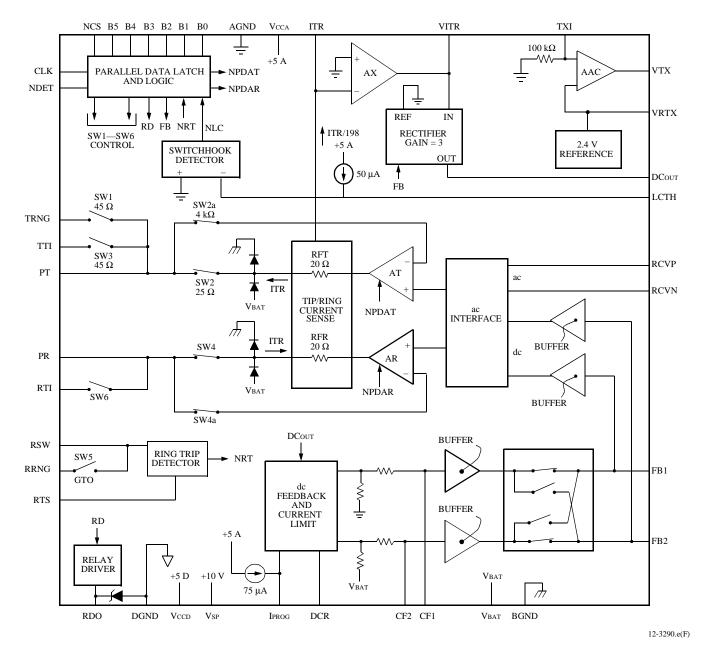

## **Architectural Diagram**

Figure 1. Architectural Diagram

## **Pin Information**

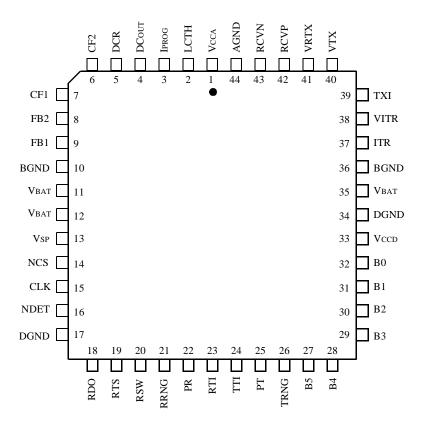

12-2571(F).f

Figure 2. 44-Pin Diagram (PLCC)

## Pin Information (continued)

### **Table 1. Pin Descriptions**

| Pin | Symbol | Туре | Name/Function                                                                                                                                                                                                                                                 |

|-----|--------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | VCCA   |      | +5 V Analog dc Supply. +5 V supply for analog circuitry.                                                                                                                                                                                                      |

| 2   | LCTH   | Ι    | Loop Closure Threshold Input. Connect a resistor to DCout to set the off-hook threshold.                                                                                                                                                                      |

| 3   | Iprog  | Ι    | Current-Limit Program Input. A resistor to DCout sets the dc current limit.                                                                                                                                                                                   |

| 4   | DCout  | 0    | <b>dc Output.</b> This output is a voltage that is directly proportional to the differential tip/ring current.                                                                                                                                                |

| 5   | DCR    | Ι    | <b>dc Resistance.</b> Ground for dc feed resistance of 180 $\Omega$ , or short to DCour for 600 $\Omega$ . Intermediate values can be set with a resistor divider from DCour to ground, the tap of which is connected to DCR.                                 |

| 6   | CF2    | I/O  | Filter Capacitor 2. Connect a 0.1 $\mu$ F, 100 V capacitor from this pin to AGND and a 0.22 $\mu$ F, 100 V capacitor from this pin to pin CF1.                                                                                                                |

| 7   | CF1    | I/O  | Filter Capacitor 1. Connect a 0.22 µF, 100 V capacitor from this pin to pin CF2.                                                                                                                                                                              |

| 8   | FB2    | Ι    | <b>Forward Battery Slowdown 2.</b> A capacitor from FB1 to AGND and from FB2 to AGND will ramp the polarity reversal transition when quiet polarity reversal is required. If not needed, the pin can be left open.                                            |

| 9   | FB1    | Ι    | <b>Forward Battery Slowdown 1.</b> A capacitor from FB1 to AGND and from FB2 to AGND will ramp the polarity reversal transition when quiet polarity reversal is required. If not needed, the pin can be left open.                                            |

| 10  | BGND   |      | Battery Ground. Ground return for the battery (VBAT) supply.                                                                                                                                                                                                  |

| 11  | VBAT   |      | Battery Supply. Negative high-voltage power supply.                                                                                                                                                                                                           |

| 12  | VBAT   |      | Battery Supply. Negative high-voltage power supply.                                                                                                                                                                                                           |

| 13  | Vsp    | _    | +10 V Supply. +10 V bias supply for switch circuitry.                                                                                                                                                                                                         |

| 14  | NCS    | Ι    | <b>Not Channel Select.</b> A low-to-high transition on this logic input stores the data on pins B0—B5 into the input latches on the SLIC. When NCS is either high or low, the SLIC is unaffected by data on pins B0—B5.                                       |

| 15  | CLK    | Ι    | Clock. Clock input.                                                                                                                                                                                                                                           |

| 16  | NDET   | 0    | <b>Not Detect.</b> When low, this logic output indicates either a ring trip or an off-hook condition, depending on the input state of the SLIC. If either the BCDMOS portion or CBIC portion of this device enters thermal shutdown, NDET will be forced low. |

| 17  | DGND   |      | Digital Ground. Ground return for VCCD and relay driver flyback current.                                                                                                                                                                                      |

| 18  | RDO    | 0    | <b>Relay Driver.</b> This output drives an external relay. RDO is low (relay operated) when a low input on B5 is latched into the SLIC.                                                                                                                       |

| 19  | RTS    | Ι    | Ring Trip Sense. Sense input for the ring trip detector.                                                                                                                                                                                                      |

| 20  | RSW    | 0    | <b>Ring Lead Ringing Access Switch.</b> Ringing relay connects this pin to pin RRNG. Connect this pin to pin PR through a 500 $\Omega$ current-limiting resistor.                                                                                             |

| 21  | RRNG   | Ι    | Ring Lead Ringing Supply. Connect this pin to the ringing supply.                                                                                                                                                                                             |

| 22  | PR     | I/O  | <b>Protected Ring.</b> The output of the ring driver and input to the transmit current sense circuit. Connect to the ring of the loop through overvoltage protection.                                                                                         |

Note: On the printed-wiring board (PWB), make the leads to BGND and VBAT as wide as possible for thermal and electrical reasons. Also, maximize the amount of PWB copper on all leads connected to this device for the lowest operating temperature.

## Pin Information (continued)

Table 1. Pin Descriptions (continued)

| Pin | Symbol | Туре | Name/Function                                                                                                                                                                |

|-----|--------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 23  | RTI    | Ι    | <b>Ring Lead Test-In.</b> Test-in relay connects this pin to PR. Connect RTI to the ring lead of the test-in bus.                                                            |

| 24  | TTI    | Ι    | <b>Tip Lead Test-In.</b> Test-in relay connects this pin to PT. Connect TTI to the tip lead of the test-in bus.                                                              |

| 25  | PT     | I/O  | <b>Protected Tip.</b> The output of the tip driver and input to the transmit current sense circuit. Connect to the tip of the loop through overvoltage protection.           |

| 26  | TRNG   | 0    | <b>Tip Lead Ringing Supply.</b> Ringing relay connects this pin to PT. Connect TRNG to the ringing supply return.                                                            |

| 27  | B5     | Ι    | Bit 5. B0—B5 determine the state of the SLIC. See Operating States.                                                                                                          |

| 28  | B4     | Ι    | Bit 4. B0—B5 determine the state of the SLIC. See Operating States.                                                                                                          |

| 29  | B3     | Ι    | Bit 3. B0—B5 determine the state of the SLIC. See Operating States.                                                                                                          |

| 30  | B2     | Ι    | Bit 2. B0—B5 determine the state of the SLIC. See Operating States.                                                                                                          |

| 31  | B1     | Ι    | Bit 1. B0—B5 determine the state of the SLIC. See Operating States.                                                                                                          |

| 32  | B0     | Ι    | Bit 0. B0—B5 determine the state of the SLIC. See Operating States.                                                                                                          |

| 33  | VCCD   | —    | +5 V Digital dc Supply. +5 V supply for logic and switch circuitry.                                                                                                          |

| 34  | DGND   |      | Digital Ground. Ground return for VCCD.                                                                                                                                      |

| 35  | VBAT   |      | Battery Supply. Negative high-voltage power supply.                                                                                                                          |

| 36  | BGND   |      | Battery Ground. Ground return for the battery (VBAT) supply.                                                                                                                 |

| 37  | ITR    | Ι    | <b>Tip/Ring Current.</b> A current output which is proportional to the differential current flowing from tip to ring. Connect a resistor from this pin to VITR.              |

| 38  | VITR   | 0    | <b>Tip/Ring Voltage Output.</b> The voltage at this output is directly proportional to the differential tip/<br>ring current. A resistor from this pin to ITR sets the gain. |

| 39  | TXI    | Ι    | Transmit ac Input. Connect a 0.1 µF capacitor from this pin to VITR.                                                                                                         |

| 40  | VTX    | 0    | <b>Transmit ac Output Voltage.</b> The ac voltage at this output is 7.2 times the ac voltage at pin TXI. The dc voltage is equal to the dc voltage on pin VRTX.              |

| 41  | VRTX   | 0    | <b>Transmit ac Reference Voltage.</b> The dc voltage at this output (2.4 V nominal) is the dc reference for the transmit signal output VTX.                                  |

| 42  | RCVP   | Ι    | <b>Receive ac Signal Input (Noninverting).</b> This high-impedance input controls the ac differential voltage on tip and ring.                                               |

| 43  | RCVN   | Ι    | <b>Receive ac Signal Input (Inverting).</b> This high-impedance input controls the ac differential voltage on tip and ring.                                                  |

| 44  | AGND   |      | Analog Ground. Ground return for VCCA.                                                                                                                                       |

Note: On the printed-wiring board (PWB), make the leads to BGND and VBAT as wide as possible for thermal and electrical reasons. Also, maximize the amount of PWB copper on all leads connected to this device for the lowest operating temperature.

## **Operating States**

The L7585 has 13 operating states. These states are selected using 4 bits, B0—B3, according to the truth table shown in Table 2. The operation of the L7585 is undefined for unassigned states. Additionally, bit B4 independently operates the test-in access contacts so that all states are available for self-test; and bit B5 independently operates a relay driver, regardless of the status of bits B0—B4. All 6 bits are loaded via the parallel data interface and chip select lead NCS.

|  |  | - | out State Coding |   |

|--|--|---|------------------|---|

|  |  |   | -                | _ |

| <b>B3</b> | B2 | <b>B1</b> | <b>B0</b> | State                                         |  |  |  |

|-----------|----|-----------|-----------|-----------------------------------------------|--|--|--|

| 1         | 1  | 1         | 1         | Forward Battery Active                        |  |  |  |

| 1         | 1  | 1         | 0         | Ground Start/Tip Open                         |  |  |  |

| 1         | 1  | 0         | 1         | Ground Start/Tip Ground                       |  |  |  |

| 1         | 1  | 0         | 0         | Forward Battery Ring Open                     |  |  |  |

| 1         | 0  | 1         | 1         | Ringing (Battery Backed)                      |  |  |  |

| 1         | 0  | 1         | 0         | Disconnect State                              |  |  |  |

| 1         | 0  | 0         | 1         | Forward Battery Low Current Ac-<br>tive State |  |  |  |

| 1         | 0  | 0         | 0         | High Impedance                                |  |  |  |

| 0         | 1  | 1         | 1         | Reverse Battery Active                        |  |  |  |

| 0         | 1  | 1         | 0         | Reverse Battery Tip Open                      |  |  |  |

| 0         | 1  | 0         | 1         | Ground Start/Tip Amplifier                    |  |  |  |

| 0         | 1  | 0         | 0         | Reverse Battery Ring Open                     |  |  |  |

| 0         | 0  | 1         | 1         | Ringing (Earth Backed)                        |  |  |  |

| 0         | 0  | 1         | 0         | Unassigned                                    |  |  |  |

| 0         | 0  | 0         | 1         | Reverse Battery Low-Current Ac-<br>tive State |  |  |  |

| 0         | 0  | 0         | 0         | High Impedance                                |  |  |  |

Table 3. B4—B5 Input State Coding

| B  | lit    | State                                         |

|----|--------|-----------------------------------------------|

| B4 | 1<br>0 | Test-in contacts off.<br>Test-in contacts on. |

| B5 | 1<br>0 | Relay driver off.<br>Relay driver on.         |

## **Forward Battery Active State**

- Normal talk and forward battery feed state.

- All circuits are powered up and active.

- Pin PT is positive with respect to pin PR (forward battery).

- SW2, SW2a, SW4, and SW4a closed; SW1, SW3, SW5, and SW6 open.

- NDET reflects the status of the switchhook detector.

## Ground Start/Tip Open State

- Ground start idle supervision state.

- Ring lead continuity test state (tone injected at the receive port) in forward battery.

- Same as forward battery active state, but with SW2 and SW2a open, and the tip drive amplifier powered down.

- Pin PT is high impedance (>100 k $\Omega$ ).

- The ring current limit is approximately equal to the value programmed for the high-current active state current limit. Current limit is achieved by reducing the ring lead voltage only (see Table 6).

- NDET indicates an off-hook when the ring current (flowing into PR) is twice the value programmed for the switchhook detector in the forward battery active state.

### **Operating States** (continued)

### **Ground Start/Tip Ground State**

- Ground start busy supervision state.

- Same as ground start/tip open state but with SW1 closed.

## Forward Battery Ring Open State

- Tip lead continuity test state (tone injected at the receive port) in forward battery.

- Same as forward battery active state, but with SW4 and SW4a open, and the ring drive amplifier powered down.

- Pin PR is high impedance (>100 k $\Omega$ ).

- Tip current limit is twice the low-current active state current limit.

- NDET indicates an off-hook when the tip current (flowing out of PT) is twice the value programmed for the switchhook detector in the forward battery active state.

## **Ringing States (2)**

- Normal ringing state.

- Tip and ring drive amplifiers are powered down.

- SW1 and SW5 closed; SW2, SW2a, SW3, SW4, SW4a, and SW6 open.

- NDET reflects the status of the ring trip detector.

- Bit B3 indicates whether the ringing voltage applied to the ringing bus is either battery backed (B3 = 1) or earth backed (B3 = 0). Although B3 has no direct effect on the state of the SLIC, it can be used by the ring trip detector to enhance ring trip detection.

### **Disconnect State**

- All circuits are powered up and active.

- SW2, SW2a, SW4, and SW4a closed; SW1, SW3, SW5, and SW6 open.

- PT and PR are at the same potential to deny current to the loop.

## Forward Battery Low-Current Active State

- Normal talk and forward battery feed state.

- All circuits are powered up and active.

- Pin PT is positive with respect to pin PR (forward battery).

- SW2, SW2a, SW4, and SW4a closed; SW1, SW3, SW5, and SW6 open.

- NDET reflects the status of the switchhook detector.

- Current limit is lowered to approximately 0.66 times the normal limit.

### **High-Impedance States (2)**

- Disconnect state.

- Tip and ring drive amplifiers are powered down (all bias currents off).

- Pins PT and PR are high impedance (>100 k $\Omega$ ).

- SW1, SW2, SW2a, SW3, SW4, SW4a, SW5, and SW6 open.

- NDET is undefined.

## **Reverse Battery Active State**

- Normal talk and reverse battery feed state.

- Same as forward battery active state, but PR is positive with respect to PT.

## **Reverse Battery Tip Open State**

- Ring lead continuity test state (tone injected at the receive port) in reverse battery.

- SW2 and SW2a open and the tip drive amplifier powered down.

- Pin PT is high impedance (>100 k $\Omega$ ).

- Pin PR is held between -1.7 V and -2.3 V for PR currents less than +-20 mA. PR current limit is the SW4 break switch current limit (250 mA < I < 85 mA).

- NDET indicates an off-hook when the ring current (flowing out of PR) is twice the value programmed for the switchhook detector in the reverse battery active state.

### **Operating States** (continued)

### **Ground Start/Tip Amplifier State**

- Current limiting is achieved by reducing ring lead voltage only. This state is the same as Ground Start/Tip Open, but with SW2 and SW2A closed and the tip amplifier powered up.

- Ring lead current limit is approximately the difference of the high-current active state limit and the current flowing out of the tip lead.

- On-hook transmission not to exceed -3 dBm with up to 5 mA flowing out of the tip lead (maximum current flow into the tip lead is permissible). Larger signal and/or current may cause distortion.

- NDET indicates an off-hook when the current flowing out of the tip plus the current flowing into the ring is twice the value programmed for the switchhook detector.

### **Reverse Battery Ring Open State**

- Tip lead continuity test state (tone injected at the receive port) in reverse battery.

- Same as reverse battery active state, but with SW4 and SW4a open, and the ring drive amplifier powered down.

- Pin PR is high impedance (>100 k $\Omega$ ).

- Tip current limit is twice the low-current active state current limit.

- NDET indicates an off-hook when the tip current (flowing into PT) is twice the value programmed for the switchhook detector in the reverse battery active state.

## **Reverse Battery Low-Current Active State**

- Normal talk and reverse battery feed state.

- Same as forward battery active state, but PR is positive with respect to PT.

- Current limit is lowered to approximately 0.66 times the normal limit.

## Absolute Maximum Ratings (TA = 25 °C)

Stresses exceeding the values listed under absolute maximum ratings may cause permanent damage to the device. This is an absolute stress rating only. Functional operation of the device at these or any other conditions in excess of those indicated in the operational sections of this data sheet is not implied. Exposure to absolute maximum rating conditions for extended periods of time may adversely affect device reliability.

| Parameter                                                   | Value                 | Unit |

|-------------------------------------------------------------|-----------------------|------|

| +5 V dc Supplies (VCCA and VCCD)                            | -0.5 to +7.0          | V    |

| +10 V dc Bias Supply (VSP)                                  | -0.5 to +15           | V    |

| Office Battery Supply (VBAT)                                | -63 to +0.5           | V    |

| Logic Input Voltage                                         | -0.5 to<br>VDDD + 0.5 | V    |

| Logic Input Clamp Diode Current,<br>per Pin                 | ±20                   | mA   |

| Logic Output Voltage                                        | -0.5 to<br>VDDD + 0.5 | V    |

| Logic Output Current, per Pin (ex-<br>cluding relay driver) | ±35                   | mA   |

| Operating Temperature Range                                 | -40 to +125           | °C   |

| Storage Temperature Range                                   | -40 to +125           | °C   |

| Relative Humidity Range                                     | 5 to 95               | %RH  |

| Ground Potential Difference<br>(BGND to AGND)               | ±3                    | V    |

| Ground Potential Difference<br>(DGND to AGND)               | ±3                    | V    |

Note: Analog voltages are referenced to AGND, digital (logic) voltages are referenced to DGND, and battery voltages are referenced to BGND. The IC can be damaged unless all ground connections are applied before and are removed after all other connections. Furthermore, when powering the device, the user must guarantee that no external potential creates a voltage on any pin of the device that exceeds the device ratings. Some of the known examples of conditions that cause such potentials during powering are the following:

1) an inductor connected to tip and ring that can force an overvoltage on VBAT through external components if the VBAT connection chatters; and 2) inductance in the VBAT lead that could resonate with the VBAT filter capacitor to cause a destructive overvoltage.

## **Electrical Characteristics**

In general, minimum and maximum values are testing requirements. However, some parameters may not be tested in production because they are guaranteed by design and device characterization. Typical values reflect the design center or nominal value of the parameter; they are for information only and are not a requirement. Minimum and maximum values apply across the entire temperature range (-40 °C to +85 °C) and entire battery range

(-35 V to -60 V). Unless otherwise specified, typical is defined as 25 °C,  $V_{CCA} = +5.0 \text{ V}$ ,  $V_{CCD} = +5.0 \text{ V}$ ,  $V_{SP} = +10 \text{ V}$ ,  $V_{BAT} = -48 \text{ V}$ . Positive currents flow into the device.

#### **Table 4. Operating Conditions and Powering**

| Parameter                                                                                              | Min  | Тур  | Max   | Unit |

|--------------------------------------------------------------------------------------------------------|------|------|-------|------|

| Temperature Range                                                                                      | -40  |      | 85    | °C   |

| Humidity Range                                                                                         | 5    |      | 95*   | %RH  |

| Supply Voltages:                                                                                       |      |      |       |      |

| VCCA                                                                                                   | 4.75 | 5.0  | 5.5   | V    |

| VCCD                                                                                                   | 4.75 | 5.0  | 5.5   | V    |

| VSP                                                                                                    | 8.0  | 10   | 12.0  | V    |

| VBAT                                                                                                   | -35  | -48  | -60   | V    |

| VCCA—VCCD                                                                                              | —    |      | ±0.5  | V    |

| Dgnd—Agnd                                                                                              |      |      | ±0.25 | V    |

| Supply Currents (all states, no loop current):                                                         |      |      |       |      |

| ICCA + ICCD (+5 V)                                                                                     |      | 4.9  | 7.0   | mA   |

| IVSP (+10 V)                                                                                           | —    | 45   | 200   | μΑ   |

| Ibat (-48 V)                                                                                           | —    | -3.1 | -4.0  | mA   |

| Total Power Dissipation (all states, no loop current)<br>(VCC = $+5$ V; VSP = $+10$ V; VBAT = $-48$ V) | _    | 175  | 200   | mW   |

| Power Supply Rejection (tip/ring and transmit) <sup>†</sup> :                                          |      |      |       |      |

| VCCA (500 Hz—3 kHz; 50 mVrms ripple)                                                                   | 30   | 40   |       | dB   |

| VCCD (500 Hz—3 kHz; 50 mVrms ripple)                                                                   | 45   |      |       | dB   |

| VSP (500 Hz—3 kHz; 250 mVrms ripple)                                                                   | 45   |      |       | dB   |

| VBAT (500 Hz—3 kHz; 50 mVrms ripple)                                                                   | 45   | —    | —     | dB   |

| Thermal <sup>†</sup> :                                                                                 |      |      |       |      |

| Thermal Resistance (still air)                                                                         | —    | —    | 47    | °C/W |

| Operating TJC                                                                                          | —    | —    | 155   | °C   |

\* Not to exceed 26 grams of water per kilogram of dry air.

† This parameter is not tested in production; it is guaranteed by design and device characterization.

#### Table 5. Ring Trip Detector

| Parameter                                                                            | Min               | Тур    | Max              | Unit            |

|--------------------------------------------------------------------------------------|-------------------|--------|------------------|-----------------|

| Voltage at input that will cause ring trip after appropriate zero crossings.         | ±2.5              | ±3     | ±3.5             | V               |

| Voltage at input that will cause immediate ring trip.                                | ±12               | ±15    | ±18              | V               |

| Ringing Source <sup>1</sup> :<br>Frequency (f)<br>dc Voltage<br>ac Voltage           | 19<br>-39.5<br>60 | 20<br> | 28<br>-57<br>105 | Hz<br>V<br>Vrms |

| Ring Trip (NDET = 0) <sup>2, 3</sup> :<br>Loop Resistance<br>Trip Time<br>NDET Valid | 2000<br>          |        | <br>200<br>80    | Ω<br>ms<br>ms   |

1. The ringing source may be either of the following:

a). The ringing source consists of the ac and dc voltages added together (battery-backed ringing); the ringing return is ground. In this case, bit B3 will always be a 1 when ringing is applied.

b). The ringing source consists of only the ac voltage (earth-backed ringing); the ringing return is the dc voltage. In this case, bit B3 will always be a 0 when ringing is applied.

2. NDET must also indicate ring trip when the ac ringing voltage is absent (<5 Vrms) from the ringing source.

3. Pretrip ringing must not be tripped by a 10 k $\Omega$  resistor in parallel with an 8  $\mu$ F capacitor applied across tip and ring.

#### **Table 6. Battery Feed Characteristics**

| Parameter                                                                                                                                                  | Symbol | Min                   | Тур                           | Max                 | Unit            |

|------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-----------------------|-------------------------------|---------------------|-----------------|

| Tip or Ring Drive Current =<br>dc + Longitudinal + Signal Currents                                                                                         | _      | 65                    |                               |                     | mA              |

| ac Signal Current                                                                                                                                          |        | 10                    |                               | —                   | mArms           |

| Longitudinal Current Capability per Wire <sup>1</sup>                                                                                                      | —      | 8.5                   | 15                            | —                   | mArms           |

| dc Loop Current Limit <sup>2</sup> (RLOOP = $100 \Omega$ ):<br>Programmability Range<br>Current Limit with VBAT = $-51.5 V$                                | Ilim   | 5                     | _                             | 45                  | mA              |

| and RPROG = 64.9 k $\Omega$<br>Low-current Mode <sup>2</sup> (RLOOP = 100 $\Omega$ ,<br>VBAT = -51.5 V, and RPROG = 64.9 k $\Omega$ )                      |        | 44<br>25              | 42<br>27.5                    | 56<br>30            | mA<br>mA        |

| Ground Start Ring Grounded (RLOOP = $100 \Omega$ )<br>Current Limit <sup>3</sup> :<br>VBAT = $-51.5 V$ , RPROG = $64.9 k\Omega$                            |        | 38                    | 43                            | 47                  | mA              |

| Loop Closure Current Detector Threshold <sup>4</sup><br>Programming Accuracy                                                                               | ILCD   |                       |                               | ±7                  | %               |

| Open Loop Voltages (DCR = 0 V):<br>Common-mode Voltage<br>Differential Voltage                                                                             | _      | <br> Vbat + 7.0       | (Vbat + 1.8)/2<br> Vbat + 6.5 | <br> Vbat + 6.0     | V<br>V          |

| Disconnect State PT/PR Voltage                                                                                                                             | PT-PR  | _                     |                               | ±100                | mV              |

| Ground Start Ring Lead Open or Shorted to Ground:<br>PT and CF1 Voltage                                                                                    | —      | -1.7                  | -2.0                          | -2.3                | v               |

| dc Feed Resistance:<br>DCR Grounded<br>DCR Connected to DCour <sup>5</sup>                                                                                 | —      | 130<br>480            | 150<br>505                    | 170<br>630          | $\Omega \Omega$ |

| dc Gains:<br>PT/PR Current to DCout Voltage <sup>6</sup> :<br>Forward Battery<br>Reverse Battery<br>DCR Voltage <sup>7</sup> to PT/PR Differential Voltage |        | -118<br>118<br>3.13   | <br>3.33                      | -132<br>132<br>3.53 | V/A<br>V/A      |

| Loop Resistance Range <sup>8</sup><br>(3.17 dBm overload into 600 $\Omega$ ):<br>ILOOP = 20 mA at VBAT = -51.5 V                                           | —      | 1890                  | 1930                          | _                   | Ω               |

| Longitudinal to Metallic Balance— <i>IEEE</i> <sup>®</sup> Std. 455:<br>50 Hz to 1 kHz<br>1 kHz to 3 kHz                                                   |        | 58 <sup>9</sup><br>48 | 70<br>66                      |                     | dB<br>dB        |

| Metallic to Longitudinal (harm) Balance:<br>200 Hz to 4 kHz                                                                                                | _      | 35                    |                               |                     | dB              |

The longitudinal current is independent of dc loop current.

1. 2. Current limit, ILIM, is programmed by a resistor, RPROG, from pin IPROG to pin DCOUT. RPROG = 1.667 x (ILIM – 4); RPROG in k $\Omega$  and ILIM in mA. The current limit versus loop voltage has a slope of 10 kΩ. The low current mode current limit is approximately 0.66 times the high current limit. The In transmission applications, for compliance with TR-57, ground start ring lead I-V characteristics at high battery, it is expected that the high-current

3. active current limit will be set to 28 mA.

Loop closure detector current, ILCD, is programmed by a resistor, RLCTH, from pin LCTH to pin DCOUT. RLCTH = 2.5 x ILCD; RLCTH in k $\Omega$  and ILCD in mA. ILCD is the tip to ring (forward battery) or ring to tip (reverse battery) current at which the loop closure detector indicates an off-hook. dc feed resistance may be adjusted between 180  $\Omega$  and 600  $\Omega$  using a resistor divider between DCOUT and DCR. The open loop differential voltage may 4.

5. also be increased by applying a negative voltage to pin DCR. See dc Gains, pin DCR. DCOUT gain depends on the resistor RGX1 from pin VITR to pin ITR. This gain assumes  $8250 \Omega$ , the recommended value. Positive current is defined as

6. before gain depends on the resistor RGAT from ph of the top ph first to ph first the differential current flowing from PT to PR. Positive voltage on pin DCR has no effect on the PT/PR voltage. At tip and ring, assuming 82.5  $\Omega$  protection resistors. At tip and ring with matched 82.5  $\Omega$  protection resistors when feedback is connected for either 600  $\Omega$  or 900  $\Omega$  termination impedance.

7.

8. 9.

#### **Table 7. Analog Signal Pins**

| DCOUT:<br>Output Offset (no loop current)<br>Output Drive Current | 0.25              |     | ±200           |            |

|-------------------------------------------------------------------|-------------------|-----|----------------|------------|

| Output Drive Current                                              |                   | _   | +200           |            |

| Output Drive Current                                              |                   |     | _200           | mV         |

|                                                                   |                   |     | -3.0           | mA         |

| Output Voltage Swing (+0.25 mA/-3 mA load):                       |                   |     |                |            |

| Maximum                                                           | VBAT              | —   | VCCA           | V          |

| Minimum                                                           | -10               |     | 0.5            | V          |

| Output Short-circuit Current                                      |                   |     | ±20            | mA         |

| Output Load Resistance                                            | 5                 | —   |                | kΩ         |

| Output Load Capacitance <sup>1</sup>                              | —                 |     | 50             | pF         |

| VITR and VTX:                                                     |                   |     | 100            | <b>X</b> 7 |

| Output Offset (no loop current) <sup>2</sup>                      | _                 |     | ±100           | mV         |

| Output Drive Current                                              | ±1                |     | —              | mA         |

| Output Voltage Swing (±1 mA load):                                | 10                |     | Varia          | 17         |

| Maximum                                                           | $-10 \pm 3.5$     | _   | VCCA           | V<br>V     |

| Minimum (VITR)<br>Minimum (VTX)                                   | $\pm 3.3$<br>-3.5 |     | <br>VCCA – 1.0 | v<br>V     |

| Minimum (VTX)<br>Output Short-circuit Current                     | -3.5              |     | $\pm 20$       | mA         |

| Output Load Resistance                                            | 4                 |     | -20            | kΩ         |

| Output Load Capacitance <sup>1</sup>                              |                   |     | 50             | pF         |

|                                                                   |                   |     | 50             | P          |

| VRTX:                                                             | 2.2               | 2.4 | 26             | V          |

| Output Voltage<br>Output Drive Current                            | $\pm 500$         | 2.4 | 2.6            | ν<br>μA    |

| Output Drive Current<br>Output Short-circuit Current              | ±300              |     | ±15            | μA<br>mA   |

| Output Load Capacitance <sup>1</sup>                              |                   |     | 50             | pF         |

| RSW:                                                              |                   |     |                | P-         |

| Impedance to Ground                                               | 3                 |     |                | MΩ         |

| DCR:                                                              |                   |     |                |            |

| Input Voltage Range <sup>3</sup>                                  | -8                |     | 0              | V          |

| Input Bias Current                                                |                   |     | ±1             | μA         |

| Input Impedance                                                   | 500               |     | —              | kΩ         |

| TXI:                                                              |                   |     |                |            |

| Input Impedance                                                   | 75                |     |                | kΩ         |

| Input Voltage Compliance                                          | ±0.4              |     |                | V          |

| Input Clamp Voltage                                               | ±0.4              |     | ±0.8           | V          |

| RCVP and RCVN:                                                    |                   |     |                |            |

| Input Voltage Range                                               | -2.5              |     | VCCA           | V          |

| Input Bias Current                                                | —                 | —   | ±1.5           | μA         |

| Input Impedance                                                   | 10                |     | —              | $M\Omega$  |

| PT and PR:                                                        |                   |     |                |            |

| Overvoltage (from external source; continuous)                    | —                 | —   | ±265           | V          |

| FB1 and FB2:                                                      |                   |     |                |            |

| ac Output Impedance                                               | —                 |     | 10             | kΩ         |

| Output Short-circuit Current                                      | ±27               |     | ±34            | μA         |

| CF1 and CF2:                                                      |                   |     |                |            |

| Output Impedance <sup>1</sup>                                     | 180               |     | 375            | kΩ         |

1. This parameter is not tested in production; it is guaranteed by design and device characterization.

2. VTX offset is measured with respect to pin VRTX.

<sup>3.</sup> Positive voltages from 0 V to VCCA are permitted at input DCR; however, voltages above 0 V have no effect on either the dc feed resistance or tip/ ring voltage.

Transmit direction is tip/ring to VTX. Receive direction is RCVP(N) to tip/ring.

#### **Table 8. Transmission Characteristics**

| Parameter                                                                                                                                                              | Min                       | Тур         | Max                           | Unit                     |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|-------------|-------------------------------|--------------------------|

| ac Termination Impedance <sup>1</sup>                                                                                                                                  | 200                       | —           | 1200                          | Ω                        |

| Return Loss <sup>2</sup> :<br>200 Hz—500 Hz<br>500 Hz—3400 Hz                                                                                                          | 25<br>29                  |             |                               | dB<br>dB                 |

| Total Harmonic Distortion (200 Hz—4 kHz) <sup>3</sup> :<br>Off-hook<br>On-hook                                                                                         |                           |             | 0.3<br>1                      | %<br>%                   |

| Transmit Gain (f = 1 kHz) <sup>4</sup> :<br>PT/PR Current to (VTX—VRTX)                                                                                                | -291                      | -300        | -309                          | V/A                      |

| Receive Gain (f = 1 kHz):<br>(RCVP—RCVN) to (PT—PR)                                                                                                                    | 1.94                      | 2           | 2.06                          | _                        |

| Gain vs. Frequency (transmit and receive) <sup>3</sup><br>(600 Ω termination; 1 kHz reference):<br>200 Hz—300 Hz<br>300 Hz—3.4 kHz<br>3.4 kHz—20 kHz<br>20 kHz—266 kHz | -0.3<br>-0.05<br>-3.0<br> | 0<br>0<br>0 | $0.05 \\ 0.05 \\ 0.05 \\ 2.0$ | dB<br>dB<br>dB<br>dB     |

| Gain vs. Level (transmit and receive; 0 dBV reference) <sup>3</sup> :<br>-50 dB to +3 dB                                                                               | -0.05                     | 0           | 0.05                          | dB                       |

| Transhybrid Loss <sup>2</sup> :<br>200 Hz—500 Hz<br>500 Hz—3400 Hz                                                                                                     | 25<br>29                  |             |                               | dB<br>dB                 |

| Idle-channel Noise (tip/ring; 600 Ω termination):<br>Psophometric<br>C-message<br>3 kHz Flat                                                                           |                           |             | -77<br>13<br>20               | dBmp<br>dBrnC<br>dBrn    |

| Idle-channel Noise ((VTX—VRTX); 600 Ω termination):<br>Psophometric<br>C-message<br>3 kHz Flat                                                                         |                           |             | -77<br>13<br>20               | dBmp0<br>dBrnC0<br>dBrn0 |

| EMC, per EN 300 386-2 and EN61000-4-6 (3 Vrms, 80% modulation, 105 kHz—80 MHz, 150 Ω source impedance) <sup>3</sup>                                                    |                           |             | -40                           | dBm, 600 Ω               |

1. Set by external components in conjunction with the T7531A/T7536 codecs. Any complex impedance R1 + R2  $\parallel$  C between 200  $\Omega$  and 1200  $\Omega$  can be synthesized.

2. Return loss and transhybrid loss are functions of device gain accuracies and the external hybrid circuit. Guaranteed performance assumes 1% tolerance external resistors and capacitors.

3. This parameter is not tested in production; it is guaranteed by design and device characterization.

4. VTX gain depends on the resistor RGX1 from pin VITR to pin ITR. This gain assumes an ideal 8250 Ω, the recommended value. Positive current is defined as the differential current flowing from PT to PR. The transmit signal at VTX is measured with respect to pin VRTX.

#### Table 9. Data Interface and Logic (Logic Inputs [CLK, NCS, and B0-B5] and Outputs [NDET])

| <b>Parameter</b> <sup>1</sup>                    | Symbol | Min        | Max  | Unit |

|--------------------------------------------------|--------|------------|------|------|

| High-level Input Voltage                         | VIH    | 2          | VCCD | V    |

| Low-level Input Voltage                          | VIL    | 0          | 0.8  | V    |

| Input Bias Current (high and low)                | Iin    | —          | ±10  | μA   |

| High-level Output Voltage (IOUT = $-100 \mu A$ ) | Voh    | VCCD - 1.5 | VCCD | V    |

| Low-level Output Voltage (IOUT = $180 \mu A$ )   | Vol    | 0          | 0.4  | V    |

| Output Short-circuit Current (Vout = VCCD)       | Ioss   | 1          | 35   | mA   |

| Output Load Capacitance <sup>2</sup>             | Col    | 0          | 50   | pF   |

1. Unless otherwise specified, all logic voltages are referenced to DGND.

2. This parameter is not tested in production; it is guaranteed by design and device characterization.

### Table 10. Timing Requirements (CLK, B0–B5, and NCS)<sup>1, 2</sup>

| Parameter                                                                        | Symbol       | Min        | Max | Unit     |

|----------------------------------------------------------------------------------|--------------|------------|-----|----------|

| CLK and NCS Rise and Fall Time (10% to 90%)                                      | tR, tF       | 0          | 50  | ns       |

| Maximum Input Capacitance                                                        | CIN          |            | 5   | pF       |

| Minimum Setup Time from B0—B5 Valid to NCS<br>$V_{IH} = 2 V$<br>$V_{IH} = 2.5 V$ | tSDS<br>tSDS | 250<br>150 |     | ns<br>ns |

|                                                                                  | tHDS<br>tHDS | 150<br>10  |     | ns<br>ns |

| Minimum Pulse Width of NCS                                                       | tWCS         | 195        |     | ns       |

| CLK Frequency                                                                    | fCLK         | 0.9        | 2.2 | MHz      |

| Minimum Pulse Width of CLK                                                       | tWCK         | 195        |     | ns       |

1. Unless otherwise specified, all times are measured from the 50% point of logic transitions.

2. These parameters are not tested in production; they are guaranteed by design and device characterization.

#### Table 11. Relay Driver (RDO)

| Parameter                                  | Symbol | Min | Max  | Unit |

|--------------------------------------------|--------|-----|------|------|

| Off-state Output Current (VRDO = VCCD)     | Ioff   |     | ±10  | μA   |

| On-state Output Voltage (IRDO = 40 mA)     | Von    | 0   | 0.60 | V    |

| On-state Output Voltage (IRDO = 20 mA)     | Von    | 0   | 0.40 | V    |

| Clamp Diode Reverse Current ( $VRDO = 0$ ) | Ir     |     | ±10  | μA   |

| Clamp Diode On Voltage (IRDO = 80 mA)      | Voc    | 6   | 20   | V    |

| Turn-on Time <sup>2</sup>                  | ton    |     | 10   | μs   |

| Turn-off Time <sup>2</sup>                 | toff   |     | 10   | μs   |

1. Unless otherwise specified, all logic voltages are referenced to DGND.

2. This parameter is not tested in production; it is guaranteed by design and device characterization.

#### Table 12. Ringing Return Access Switch (SW1)

| Parameter                                                    | Min | Тур | Max              | Unit |

|--------------------------------------------------------------|-----|-----|------------------|------|

| Off-state:                                                   |     |     |                  |      |

| Maximum Differential Voltage                                 |     |     | $\pm 320^{1}$    | V    |

| dc Leakage Current (VSW = $\pm 320$ V)                       |     |     | ±10              | μA   |

| Feedthrough Capacitance <sup>2</sup>                         | —   | —   | 15               | pF   |

| On-state (See On-State Switch V-I Characteristics section.): |     |     |                  |      |

| Resistance (RON)                                             |     | 45  | 90               | Ω    |

| Maximum Differential Voltage (Vmax)                          |     |     | 320 <sup>1</sup> | V    |

| Foldback Voltage Breakpoint 1 (V1)                           | 120 |     |                  | V    |

| Foldback Voltage Breakpoint 2 (V2)                           | 200 |     |                  | V    |

| Current Limit (ILIMIT1)                                      | 120 | 220 | 360              | mA   |

| Current Limit (ILIMIT2)                                      | 2   | —   | —                | mA   |

| dV/dT Sensitivity <sup>2, 3</sup>                            |     | 200 | 2000             | V/µs |

1. At 25 °C, maximum voltage rating has a temperature coefficient of +0.167 V/°C.

2. This parameter is not tested in production; it is guaranteed by design and device characterization.

3. Applied voltage is 100 Vp-p square wave at 100 Hz to measure dV/dt sensitivity at 200 V/µs typical with no switch turn-on. In the case of dV/dt induced turn-on at higher dV/dt and amplitude, the design objective is no damage to at least 2000 V/µs and full voltage. A known condition that can cause damage is initial current flow prior to the application of the dV/dt and the sudden application of reverse bias with dV/dt induced switch turn-off. In this case, no damage shall occur for dV/dt up to 2000 V/µs as guaranteed by design and characterization.

#### Table 13. Test-In Access Switches (SW3 and SW6)

| Parameter                                                    | Min | Тур | Max           | Unit |

|--------------------------------------------------------------|-----|-----|---------------|------|

| Off-state:                                                   |     |     |               |      |

| Maximum Differential Voltage                                 |     |     | $\pm 320^{1}$ | V    |

| dc Leakage Current (VSW = $\pm 320$ V)                       |     | —   | ±10           | μA   |

| Feedthrough Capacitance <sup>2</sup>                         |     |     | 15            | pF   |

| On-state (See On-State Switch V-I Characteristics section.): |     |     |               |      |

| Resistance (RON)                                             |     | 45  | 90            | Ω    |

| Maximum Differential Voltage (Vmax)                          |     |     | 60            | V    |

| Current Limit (ILIMIT) Switches SW3 and SW6 <sup>3</sup>     | 85  | —   | —             | mA   |

| dV/dT Sensitivity <sup>2, 4</sup>                            |     | 200 | 2000          | V/µs |

1. At 25 °C, maximum voltage rating has a temperature coefficient of +0.167 V/°C.

2. This parameter is not tested in production; it is guaranteed by design and device characterization.

3. Test in access switches current limit will be > tip and ring break switches current limit.

4. Applied voltage is 100 Vp-p square wave at 100 Hz to measure dV/dt sensitivity at 200 V/µs typical with no switch turn-on. In the case of dV/dt induced turn-on at higher dV/dt and amplitude, the design objective is no damage to at least 2000 V/µs and full voltage. A known condition that can cause damage is initial current flow prior to the application of the dV/dt and the sudden application of reverse bias with dV/dt induced switch turn-off. In this case, no damage shall occur for dV/dt up to 2000 V/µs as guaranteed by design and characterization.

#### Table 14. Tip and Ring Break Switches (SW2 and SW4)

| Parameter                                                    | Min         | Тур | Max           | Unit |

|--------------------------------------------------------------|-------------|-----|---------------|------|

| Off-state:                                                   |             |     |               |      |

| Maximum Differential Voltage                                 | —           |     | $\pm 320^{1}$ | V    |

| dc Leakage Current (Vsw = $\pm 320$ V)                       |             | —   | ±20           | μA   |

| Feedthrough Capacitance <sup>2</sup>                         |             | —   | 50            | pF   |

| On-state (See On-State Switch V-I Characteristics section.): |             |     |               |      |

| Resistance (Ron)                                             |             | 25  | 50            | Ω    |

| Maximum Differential Voltage (Vmax)                          | —           | —   | $320^{1}$     | V    |

| Foldback Voltage Breakpoint 1 (V1)                           | 60          | —   |               | V    |

| Foldback Voltage Breakpoint 2 (V2)                           | $V_1 + 0.5$ | —   |               | V    |

| Current Limit (ILIMIT1)                                      | 85          | 160 | 250           | mA   |

| Current Limit (ILIMIT2)                                      | 2           | —   | —             | mA   |

| dV/dT Sensitivity <sup>2, 3</sup>                            | —           | 200 | 2000          | V/µs |

1. At 25 °C, maximum voltage rating has a temperature coefficient of +0.167 V/°C.

2. This parameter is not tested in production; it is guaranteed by design and device characterization.

3. Applied voltage is 100 Vp-p square wave at 100 Hz to measure dV/dt sensitivity at 200 V/ $\mu$ s typical with no switch turn-on. In the case of

dV/dt induced turn-on at higher dV/dt and amplitude, the design objective is no damage to at least 2000 V/µs and full voltage. A known condition that can cause damage is initial current flow prior to the application of the dV/dt and the sudden application of reverse bias with dV/dt induced switch turn-off. In this case, no damage shall occur for dV/dt up to 2000 V/µs as guaranteed by design and characterization.

#### Table 15. Tip and Ring Feedback Switches (SW2a and SW4a)

| Parameter                                                    | Min | Тур | Max              | Unit |

|--------------------------------------------------------------|-----|-----|------------------|------|

| Off-state:                                                   |     |     |                  |      |

| Maximum Differential Voltage                                 |     |     | $\pm 320^{1}$    | V    |

| dc Leakage Current (Vsw = $\pm 320$ V)                       | —   | —   | ±10              | μA   |

| Feedthrough Capacitance <sup>2</sup>                         |     | —   | 15               | pF   |

| On-state (See On-State Switch V-I Characteristics section.): |     |     |                  |      |

| Resistance (Ron)                                             |     | 4   | 10               | kΩ   |

| Maximum Differential Voltage (Vmax)                          |     |     | 320 <sup>1</sup> | V    |

| Current Limit (ILIMIT)                                       | 0.5 |     | 20               | mA   |

| dV/dT Sensitivity <sup>2, 3</sup>                            |     | 200 | 2000             | V/µs |

1. At 25 °C, maximum voltage rating has a temperature coefficient of +0.167 V/°C.

2. This parameter is not tested in production; it is guaranteed by design and device characterization.

3. Applied voltage is 100 Vp-p square wave at 100 Hz to measure dV/dt sensitivity at 200 V/µs typical with no switch turn-on. In the case of dV/dt induced turn-on at higher dV/dt and amplitude, the design objective is no damage to at least 2000 V/µs and full voltage. A known condition that can cause damage is initial current flow prior to the application of the dV/dt and the sudden application of reverse bias with dV/dt induced switch turn-off. In this case, no damage shall occur for dV/dt up to 2000 V/µs as guaranteed by design and characterization.

#### Table 16. Ringing Access Switch (SW5)

| Parameter                                                    | Min | Тур | Max     | Unit |

|--------------------------------------------------------------|-----|-----|---------|------|

| Off-state:                                                   |     |     |         |      |

| Maximum Differential Voltage                                 | —   | —   | ±475    | V    |

| dc Leakage Current (Vsw = $\pm 500$ V)                       | —   | —   | ±20     | μA   |

| dc Leakage Current (VsW = $\pm 250$ V)                       |     | —   | $\pm 1$ | μA   |

| Feedthrough Capacitance <sup>1</sup>                         | —   | 1   | —       | pF   |

| On-state (See On-State Switch V-I Characteristics section.): |     |     |         |      |

| Crossover Offset Voltage (Vos; $ISW = \pm 1 mA$ )            |     |     | 3       | V    |

| Resistance (RON)                                             |     | —   | 10      | Ω    |

| Surge Current (10 µs x 1000 µs pulse) <sup>1</sup>           |     | —   | 2.5     | А    |

| Release Current <sup>1</sup>                                 | 0.1 | —   | 2       | mA   |

| dV/dT Sensitivity <sup>1, 2</sup>                            | _   | 200 | 2000    | V/µs |

| Common-mode Voltage (Maximum Either Switch Terminal with Re- | —   | _   | 320     | V    |

| spect to Ground)                                             |     |     |         |      |

1. This parameter is not tested in production; it is guaranteed by design and device characterization.

2. Applied voltage is 100 Vp-p square wave at 100 Hz to measure dV/dT sensitivity.

3. Applied voltage is 100 Vp-p square wave at 100 Hz to measure dV/dt sensitivity at 200 V/ $\mu$ s typical with no switch turn-on. In the case of

dV/dt induced turn-on at higher dV/dt and amplitude, the design objective is no damage to at least 2000 V/µs and full voltage. A known condition that can cause damage is initial current flow prior to the application of the dV/dt and the sudden application of reverse bias with dV/dt induced switch turn-off. In this case, no damage shall occur for dV/dt up to 2000 V/µs as guaranteed by design and characterization.

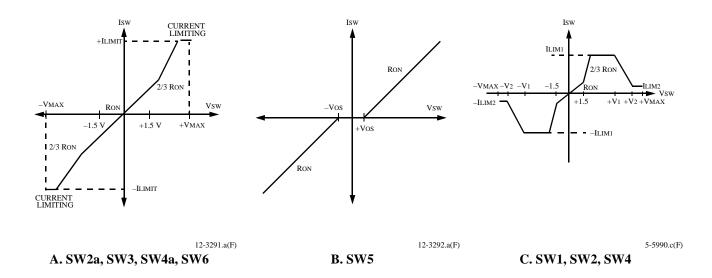

## **On-State Switch I-V Characteristics**

Figure 3. On-State Switch I-V Characteristics

## Applications

### **Tip/Ring Protection**

The L7585 SLIC has integrated overvoltage tertiary protection diodes in the tip and ring paths. The device also has an integrated thermal shutdown circuit which places tip/ring drivers in a high-impedance state when the die temperature exceeds 160 °C.

The SLIC requires the following to survive lightning and power cross requirements:

- Fusible elements or PTCs

- Current-limiting resistors

- A secondary protector

Thermal fuse/surge resistor modules that satisfy the various requirements can be purchased from  $MMC^{TM}$ . Protection resistors should have a tolerance of  $\pm 1\%$  and a ratio tolerance of  $\pm 0.5\%$ . The suppressor breakover voltage of the secondary protector should be set as low as possible. Select a value just above the maximum peak ring signal and maximum battery voltage.

### **NDET Under Fault Condition**

- The state of NDET is not guaranteed with loss of battery.

- In the ringing state, RRNG floating or with only dc on the ringing source, NDET will produce an off-hook because there are not zero crossings of ringing to cause an onhook.

- In the ringing state with only ac (>40 Vrms) on the ringing source, an on-hook will be produced after the second zero crossing of the ringing waveform, because there is no dc component to the ringing current.

- In the ringing state, if the resistor between RSW and PR is open, there will likely be a large voltage at the ringing

input (due to capacitive loading) and ring trip will be asserted after the second zero crossing of ringing. Because there is no guarantee of the load at PR in this condition, there can be no guarantee of the state on NDET in this condition.

If the device enters into thermal shutdown due to a fault that causes an off-hook, the off-hook indication will be stable as the device cycles in and out of thermal shutdown. If the fault does not cause an off-hook, NDET will cycle between on- and off-hook as the device cycles in and out of thermal shutdown.

### Power, Clocking, and Layout

The SLIC requires +5 V (VCCA and VCCD) and a negative battery voltage (VBAT) to operate. The integrated switches require a 10 V or 12 V supply (VSP) and a TTL clock (CLK) to operate. CLK requires a frequency between 1.0 MHz to 2.048 MHz with a 50% duty cycle. SW1, SW3, and SW6 will not operate without CLK applied.

A four- or six-layer board is recommended. Analog and battery grounds should be laid out as a plane and a layer, and tied together at the device. Digital ground can also be tied to this plane or run separately. Vsp is referenced to DGND. Vcc can be run as individual traces and can reside on the same layer as signal paths. VccA and VccD can be tied together at the SLIC. Placement of the talk battery is not critical.

The ring bus should be on a separate layer from the SLIC/ codec interface signal leads and traces should run perpendicular if the traces must cross. TXI, VITR, and ITR are the sensitive nodes on the SLIC. Transmit runners should be run in pairs, and receive runners should be run in pairs between the SLIC and the codec. A channel-to-channel spacing should be maintained.

### Applications (continued)

### **Ring Trip**

Ring trip is set by the value of RS1.

The ring trip threshold at the ring trip inputs is  $\pm 2.5$  V minimum,  $\pm 3.5$  V maximum.

A resistor value of 500  $\Omega$ , as shown in Figure 4, will set the ring trip current threshold to  $\pm 6.0$  mA typical.

Ring trip is asserted upon entering the ringing mode until the second zero crossing of ringing. This is either a positive-going zero crossing between -40 V and -30 V at -50 V VBAT) or a negative-going zero crossing (between -10 V and -20 V at -50 V VBAT). The different threshold for positive-going and negative-going zero crossings is the result of hysteresis of approximately 20 V.

Ring trip will not be asserted unless the ring trip threshold is exceeded for two zero crossings. This is either a positivegoing zero crossing between -40 V and -30 V at -50 V VBAT) or a negative-going zero crossing (between -10 V and -20 V at -50 V VBAT). The different threshold for positivegoing and negative-going zero crossings is the result of hysteresis of approximately 20 V.

Note that since the ringing voltage is monitored at RSW, one zero crossing can occur at switch turn-on depending on initial conditions.

Ring trip is asserted immediately if the ring trip input is 15 V  $\pm$  3 V.

### **False On-Hook Transients**

- If the L7585F is off-hook in the ground-start/tip open state, the ground-start/tip ground state, or the ground-start/tip amplifier state, due to an applied ring ground, and it is switched to the forward battery active state, it will not generate a false on-hook longer than 10 ms in duration. This applies for loop resistances of 0 Ω to 2000 Ω, providing that all of the following criteria are satisfied:

- A loop closure is applied before the L7585F switches to the forward battery active state.

- The loop closure resistance (telephone set) is less than 430  $\Omega$ .

- The ring ground and loop closure are applied at the same end of the loop.

- If the ring ground is removed while the L7585F is in the forward battery active state, then the ring ground resistance must be greater than 225 Ω when the dc current limit is 40 mA, or greater than 430 Ω when the dc current is 28 mA.

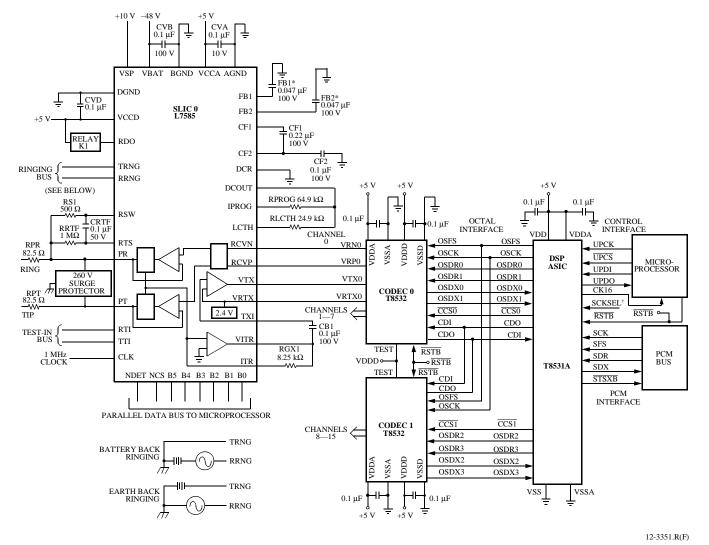

## **Application Diagram**

\* Optional for quiet reverse battery.

† 4.096 MHz operation; for 2.048 MHz operation, tie SCKSEL to Vss.

Figure 4. 16-Channel Line Card Solution

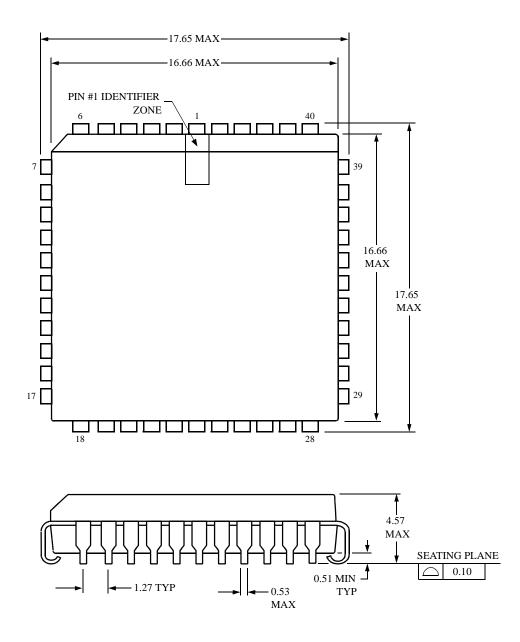

## **Outline Diagram**

## 44-Pin PLCC

Dimensions are in millimeters.

**Note:** The dimensions in this outline diagram are intended for informational purposes only. For detailed schematics to assist your design efforts, please contact your Agere Communications Sales Representative.

5-2506(F)r7

# **Ordering Information**

| Device Part No. | Description                                | Package                              | Comcode   |

|-----------------|--------------------------------------------|--------------------------------------|-----------|

| LUCL7585FP-D    | Full-Feature, Low-Power SLIC<br>and Switch | 44-Pin PLCC (Dry Bag)                | 108417023 |

| LUCL7585FP-DT   | Full-Feature, Low-Power SLIC<br>and Switch | 44-Pin PLCC (Tape and Reel, Dry Bag) | 108417031 |

*IEEE* is a registered trademark of The Institute of Electrical and Electronics Engineers, Inc. *MMC* is a trademark of Microelectronic Modules Corporation.

Legerity, Inc. reserves the right to make changes to the product(s) or information contained herein without notice. No liability is assumed as a result of their use or application.

Copyright © 2001 Legerity, Inc. All Rights Reserved

September 2001 DS01-312ALC (Replaces DS00-216ALC)